## 16. DISEÑO DEL GDP-32<sup>II</sup>

| 16.1 | CARACTERÍSTICAS BÁSICAS DE DISEÑO                                                                                                                                                                       | 2                    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 16.2 | FORMA DEL RECEPTOR                                                                                                                                                                                      | 4                    |

| 16.3 | CARD-PC MPU BOARD                                                                                                                                                                                       | 8                    |

| 16.4 | BD287 PLACA DEL PANEL FRONTAL                                                                                                                                                                           | 8                    |

| 16.5 | BD183 ANALOG BOARD                                                                                                                                                                                      | 10                   |

|      | Funciones del Relé  Amplificador Diferencial  DAC de Compensación  Filtro de Paso de Banda de La Línea de Alimentación  Etapas de Ganancia  Filtro Anti-Alias  Multiplexor  Analog-To-Digital Converter | 10<br>13<br>13<br>13 |

| 16.6 | PLACA DE CALIBRACIÓN Y SINCRONIZACIÓN                                                                                                                                                                   | 18                   |

|      | SECCIÓN DE CALIBRADO Y MULTIPLEXORÓHMETRO<br>SECCIÓN DE SINCRONIZACIÓN                                                                                                                                  | 18                   |

| 16.7 | EL COMPARTIMENTO DE LA BATERÍA                                                                                                                                                                          | 23                   |

|      | DISEÑO EN CAJA PEQUEÑA (GDP-32 <sup>II</sup> T)<br>DISEÑO DE CAJA GRANDE                                                                                                                                |                      |

| 16.8 | EL OSCILADOR DE CRISTAL                                                                                                                                                                                 | 23                   |

#### 16.1 CARACTERÍSTICAS BÁSICAS DE DISEÑO

Una completa descripción de las características externas del GDP-32<sup>II</sup> puede encontrarse en la *Sección 2 – Descripción del receptor GDP-32<sup>II</sup>*.

La caja del GDP-32<sup>II</sup> se divide en dos secciones: Analógica y Digital. Estas secciones están separadas para minimizar la captación de ruido y para facilitar la solución de problemas y las reparaciones.

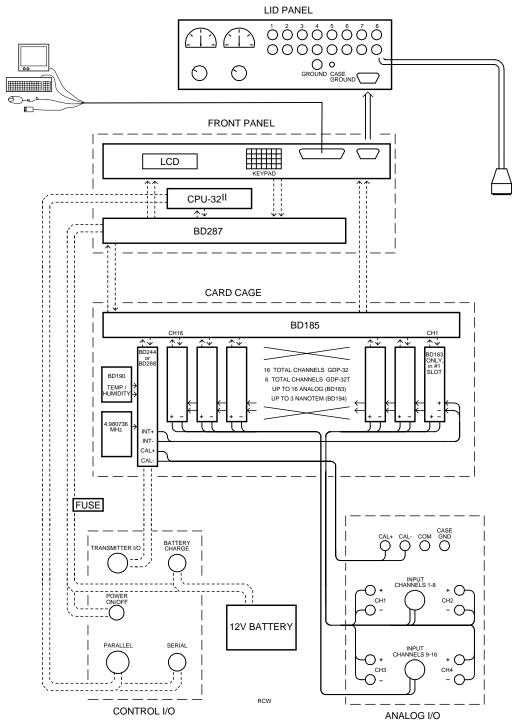

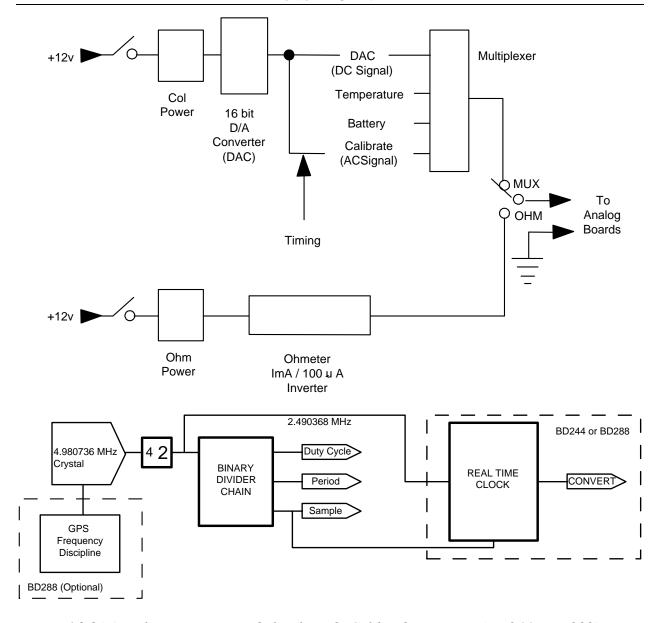

Figura 16.1 (a) - GDP-32<sup>II</sup> Diagrama de Bloques 1

Figura 16.1 (b) - GDP-32 $^{II}$  Diagrama de Bloques 2

#### 16.2 FORMA DEL RECEPTOR

Las figuras 16.1 (a) y (b) son diagramas de bloques detallados de la forma general del receptor. El diseño separa las placas del circuito digital de control montadas en el panel frontal de las tarjetas analógicas de adquisición y de la tarjeta de calibrado insertadas en la caja de tarjetas.

El sistema analógico del GDP-32<sup>II</sup> consta del Panel Analógico I/O Panel a través del cual las señales se conectan con 16 tarjetas analógicas. Las tarjetas analógicas proporcionan la ganancia necesaria y filtran antes de la conversión A/D. Van montadas junto con la tarjeta de calibrado y cronometraje.

Cada tarjeta analógica contiene:

- Alimentación individual

- Circuito de muestra y toma de datos de alta velocidad

- Convertidor Analógico/Digital (ADC)

La tarjeta de calibrado y cronometraje contiene:

- Las cadenas contadoras que generan frecuencias de detección binarias seleccionables desde los menús de programa.

- El convertidor Digital/Analógico (DAC) para generar señales analógicas de prueba para poder realizar calibraciones.

- Circuitería de sincronización por GPS (BD 288)

Los cables de cinta, situados entre el panel frontal y la tapa, envían las señales analógicas amplificadas y filtradas desde cada placa analógica al interruptor de medida del panel.

Un oscilador de cristal de frecuencia 4.980736 MHz estabilizado por calentadores va montado directamente a la placa de cronometraje (BD244 or BD288) en la caja grande GDP-32<sup>II</sup>. En la caja pequeña GDP-32<sup>II</sup>, el cristal va montado al lado del compartimento de la batería.

El control básico y la monitorización de la función del receptor se hace a través del teclado y del display LCD del panel frontal. Montado en la parte de abajo del panel hay una tarjeta simple de PC 66 MHz 586 junto con la placa madre (BD287). El conjunto del panel frontal consta del Panel Frontal, la placa MPU y BD287, y constituye un completo sistema de control digital de adquisición analógica de datos.

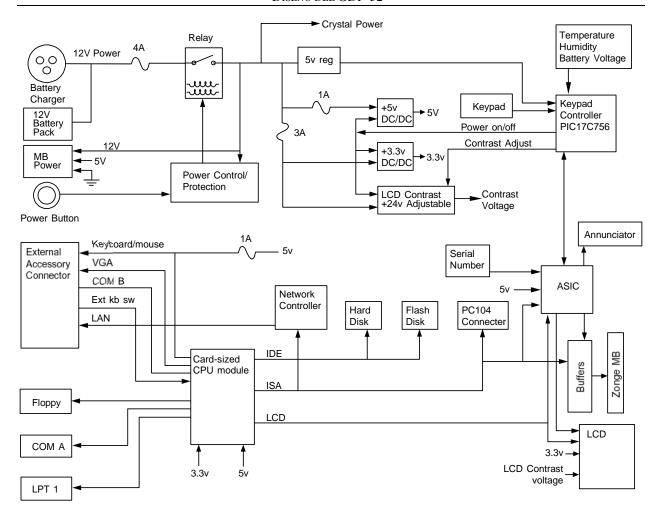

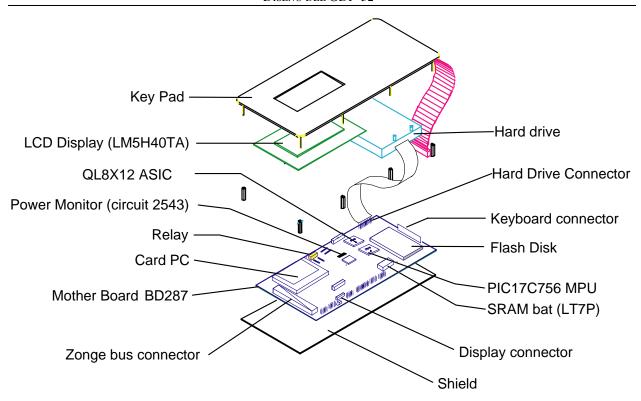

Figura 16.2(a) - Esquema del montaje del Panel Frontal

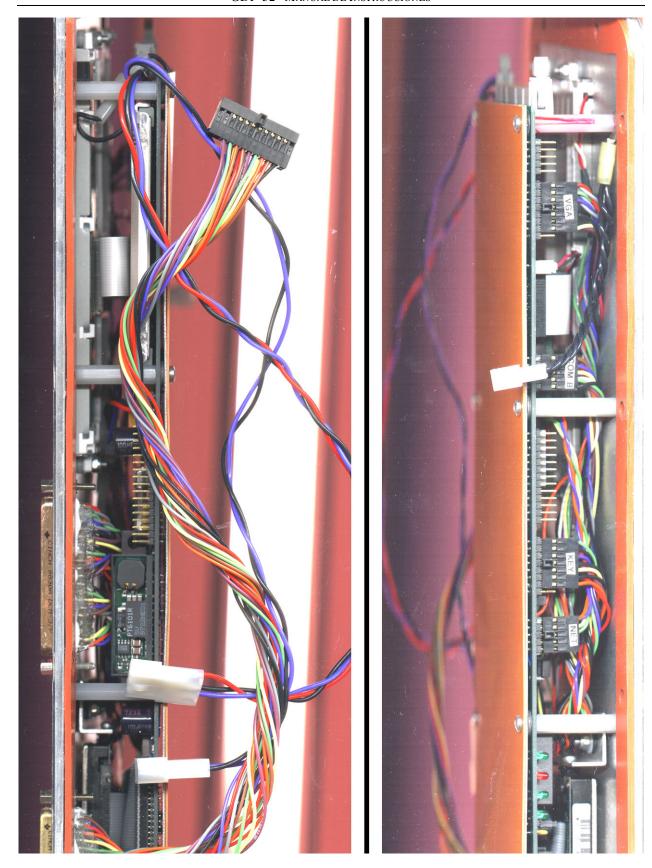

Figura 16.2 - Foto del Panel Frontal -(b) Parte trasera, (c) Parte Frontal

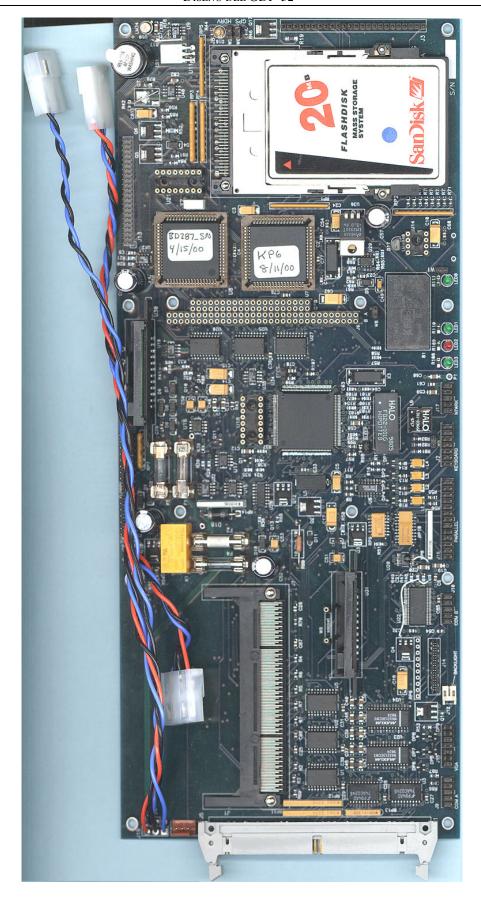

Figura 16.3 – BD287 incluyendo la memoria flash (arriba) y la ranura de la tarjeta (abajo)

#### 16.3 CARD-PC MPU BOARD

La tarjeta AMD 586 - PC MPU va montada en el BD287 y está debajo del display LCD. Esta placa es un microprocesador 586 AMD que funciona a 66 MHz. La tarjeta MPU contiene:

- Un puerto de impresión

- Dos puertos serie

- Un puerto de teclado / ratón

- Interfaces CRT y LCD

- IDE interfaz

Cuando se configura para el GDP-32<sup>II</sup>, la tarjeta contiene 16 Mb de DRAM. La tarjeta Card-PC se conecta con los periféricos a través de un bus compatible ISA que se usa para conectar al BD287 del cual se habla a continuación.

#### 16.4 BD287 PLACA DEL PANEL FRONTAL

El módulo Card-PC MPU conecta directamente al BD287 a través de su conector bus EASI. BD287 patentado por Zonge Engineering.

La placa BD287 contiene:

- Todos los decodificadores I/O

- Memoria flash para almacenamiento de programas, memorias cachés de datos y de calibración

- decodificador con teclado numérico

- anunciador

- circuitos de monitorización de energía

- suministro de energía para los circuitos digitales y para la interfaz LAN

La memoria flash retiene datos durante largos periodos de tiempo incluso cuando el GDP-32<sup>II</sup> está apagado. La capacidad de la memoria flash es suficiente para retener muchos días de datos en condiciones normales de uso. Las series de datos en el tiempo obtenidas al ejecutar el programa AMT/MT se almacenan en el disco duro.

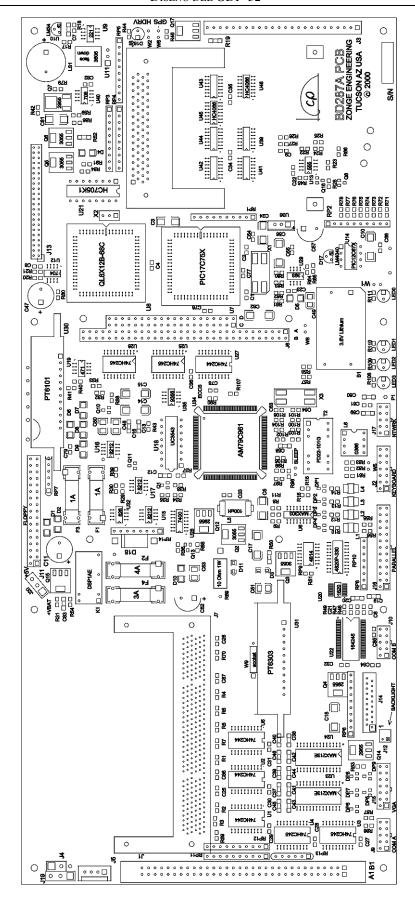

Figura 16.4 - Esquema de la placa BD287 del Panel Frontal

#### 16.5 BD183 ANALOG BOARD

El formato de caja pequeña del GDP-32<sup>II</sup>T dispone de una capacidad de la placa analógica de 6 canales. El GDP-32<sup>II</sup> con caja grande tiene una capacidad de placa analógica de 16 canales. El GDP-32<sup>II</sup> usa una placa para cada canal activo. Las placas se instalan (hasta lo que permita la capacidad de la caja) en ranuras consecutivas, empezando con la ranura 1, la ranura más a la derecha de la caja de tarjetas analógicas.

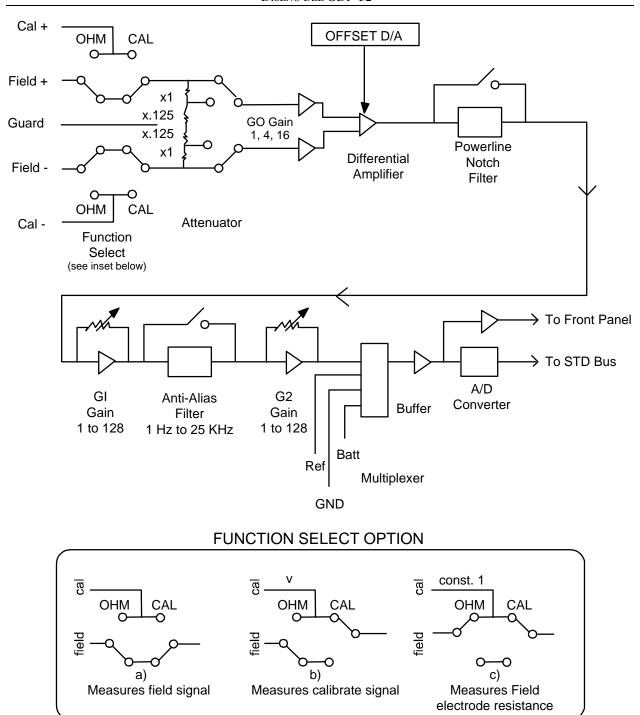

Cada placa analógica lleva un número de posibilidades para configurar relé, ganancia, filtro y DAC. Se necesita entender parte de la ruta de la señal para controlar la placa. La ruta de la señal va a través de una serie de relés a la etapa del *Amplificador de Ganancia* búfer/diferencial (G0), luego al *Quad-Notch Filter* (BP), etapa de Amplificador de Ganancia (G1), *Filtro Antialias*, etapa o estados de Amplificador de Ganancia (G2), *Multiplexor*, y *ADC* (ver *Figura 16.5* (a)).

#### **FUNCIONES DEL RELÉ**

Hay tres configuraciones de entrada:

- 1. Los relés de Calibración y del Óhmetro están abiertos, permitiendo medir la señal de campo.

- 2. El *Relé de Calibración* está cerrado, proporcionando de ese modo a la placa Analógica una señal calibrada procedente de la placa de Cronometraje/Calibrado para auto-calibración.

- 3. Los dos relés, el del *Óhmetro* y el de Calibrar, están cerrados, permitiendo que una corriente constante (100 µa generados en la placa de calibrado) fluya al panel Analógico I/O y a los electrodos de campo. Esto permite la medida de las resistencias de contacto de los electrodos para cada par de electrodos.

El relé del *Atenuador* ofrece una resistencia atenuadora a la ruta de la señal para reducir el nivel de la señal de entrada en un factor de 0.125.

**NOTA:** El uso del atenuador puede causar cambios en la fase a frecuencias por encima de 1 kHz debido a un incremento del valor de la constante de tiempo RC. Dado que este desfase es función de la resistencia de carga y no puede eliminarse eficazmente, el atenuador sólo se usa a altas frecuencias cuando es absolutamente necesario.

#### AMPLIFICADOR DIFERENCIAL

El amplificador diferencial de entrada presenta una alta impedancia para la señal de entrada para minimizar la pérdida de señal y la distorsión. El amplificador diferencial combina señales para minimizar voltajes en modo común.

#### DAC DE COMPENSACIÓN

La salida de un *Convertidor Digital-a-Analógico* (DAC) es proporcionada a cada placa del BD183. Esta salida compensa cualquier nivel de señal DC (tal como el SP) que aparezca en la señal de entrada.

El Convertidor Digital a Analógico (DAC) acepta una palabra digital del MPU y produce un voltaje analógico. El máximo valor de compensación es  $\pm 2.5$  voltios.

Figura 16.5 (a) - Bloque Diagrama de una Placa Analógica

Figura 16.5(b) - Placa Analógica, BD183D

#### FILTRO DE PASO DE BANDA DE LA LÍNEA DE ALIMENTACIÓN

Se puede configurar para rechazar los armónicos fundamental, 3°, 5° y 9°, u otra combinación de 4 frecuencias de armónicos deseadas.

Por ejemplo en un país con frecuencia de la corriente de 50 Hz, los filtros estándar suministrados rechazarán 50, 150, 250 y 450 Hz. Los filtros están configurados de modo que se puedan activar sólo los filtros de 50 y 150 Hz, o los 4 simultáneamente. Los filtros pueden también prepararse para aplicaciones en el dominio del tiempo y para funcionar en áreas tranquilas. Tenga en cuenta que usar estos filtros puede causar distorsiones de fase y amplitud alrededor de las frecuencias de rechazo. Esa distorsión puede eliminarse por calibración con los filtros habilitados.

#### ETAPAS DE GANANCIA

Tres etapas de ganancia del amplificador, G0, G1, y G2 proporcionan la ganancia de la señal disponible en la tarjeta. G1 y G2 usan pasos de ganancia binaria del 1 al 128 dando una ganancia total del sistema de 16,384. Sin embargo, durante el funcionamiento del programa las etapas de ganancia están limitadas al rango de 1 a 64 cada una, para una ganancia total del sistema de 4096. En la etapa de ganancia G0 se pueden seleccionar ganancias de 1, 4, y 16, para una ganancia total máxima de 65,536.

#### FILTRO ANTI-ALIAS

Este filtro de paso bajo sintonizable se usa para atenuar las frecuencias de la señal por encima de la banda de paso deseada. Hay dos grupos de frecuencia disponibles y se seleccionan como grupo LO o HI. El grupo bajo abarca de 1 Hz a 255 Hz en incrementos de 1 Hz mientras que el grupo de alta abarca de 100 Hz a 25.5 kHz en incrementos de 100 Hz. Un filtro alias de bypass también se incluye para pruebas de diagnóstico.

#### **MULTIPLEXOR**

Esta etapa selecciona una de las cuatro posibilidades de entrada y presenta la selección del ADC para conversión. Las selecciones son como siguen:

- 1. **Analógica** La salida de los amplificadores de señal es suministrada al ADC. Esta es la condición normal.

- 2. **Referencia** El voltaje de referencia analógico del ADC es proporcionado al ADC que normalmente representa una escala natural de 32767.

- 3. **Tierra** La tierra analógica está conectada al ADC y debería ser 0.

- 4. Batería Un voltaje de 0.1 veces el actual voltaje de 12 voltios de la batería se presenta al ADC para que no sea necesario atenuador. El voltaje mostrado se multiplica por 10 y entonces representa el voltaje actual de la batería.

#### ANALOG-TO-DIGITAL CONVERTER

El conversor (ADC) convierte la señal analógica recibida a formato digital que se almacena en la memoria del ordenador junto con otros parámetros de la tarjeta.

Antes de que las señales de voltaje analógicas puedan procesarse digitalmente, primero deben ser correctamente muestreadas y convertidas a formato digital usando un ADC. Se emplea un ADC de 16 bit para esto en las placas analógicas estándar BD183. Esto significa que hay 65,536 estados de salida posibles en las 16 líneas de salida digital. En el GDP, los estados se establecen de manera que 32,767 cuentas indica voltaje a escala real positiva, 0 indica cero voltios y -32,768 indica voltaje en escala real negativa. Los valores de la escala real se determinan por el voltaje de referencia (4.5 voltios). Por ejemplo, si un voltaje desconocido sale con 7282 cuentas, multiplique 7282 por 4.5 (voltaje de referencia) y divida por 32767. La forma de la ecuación para convertir cuentas digitales a voltios es:

$$volts = \frac{4.5}{32767} counts$$

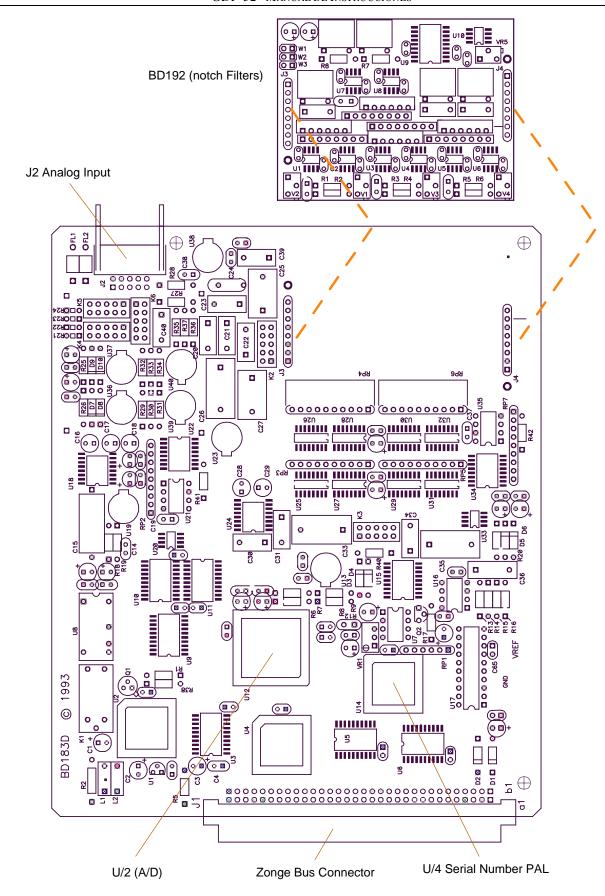

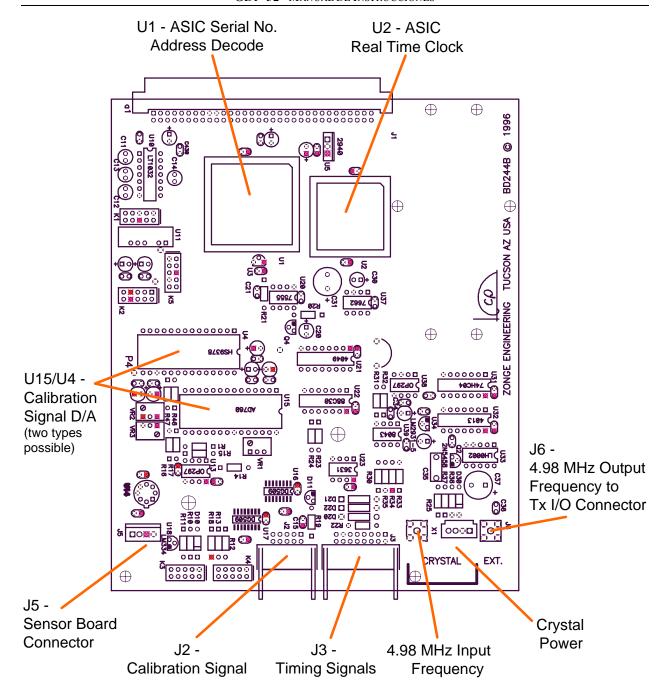

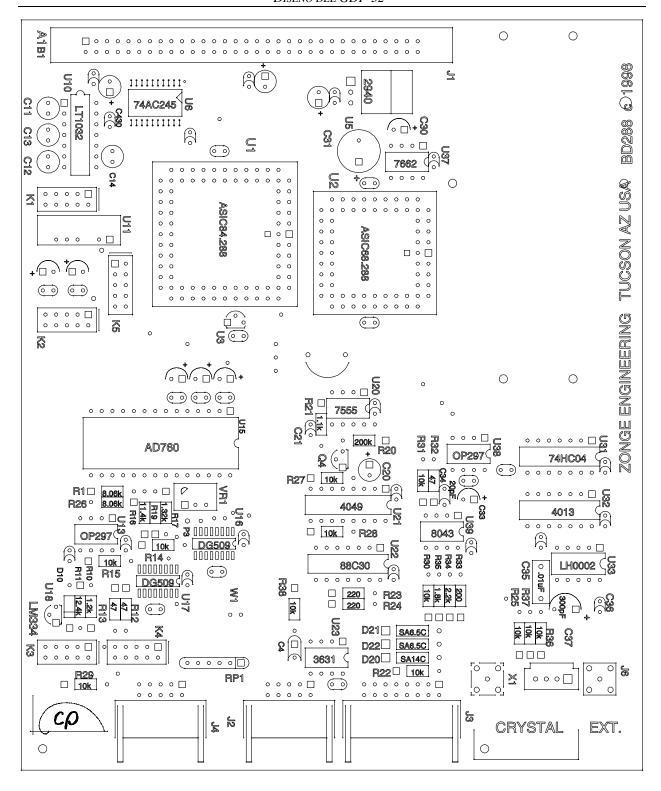

Figura 16.6 (a) – Bloque Diagrama de la Placa de Calibrado y Tiempo (BD244 o BD288)

Figura 16.6 (b) - Placa de Calibrado y Tiempo, BD244

Figura 16.6 (c) - Placa de Calibrado y Sincronización o Medida del Tiempo(Cronómetro), BD288

#### 16.6 PLACA DE CALIBRACIÓN Y SINCRONIZACIÓN

Cada receptor GDP-32<sup>II</sup> contiene una placa de Calibrado y Sincronización (BD244 o BD288) situada en la caja de la tarjeta analógica. La *Figura 16.6 (a)* es un diagrama de bloques simplificado que muestra los principales elementos funcionales de la placa. Las tres secciones o funciones principales son: Calibraje, Óhmetro (para chequear la resistencia de contacto), y Sincronización o Cronometraje.

#### SECCIÓN DE CALIBRADO Y MULTIPLEXOR

La sección de calibrado consta de una señal AC y un nivel de voltaje DC de un DAC de 16-bit, y sensores de temperatura y humedad. Todos esos componentes se encaminan a cada uno de los canales analógicos. Bajo control del software del GDP-32<sup>II</sup> la sección de calibrado soporta las siguientes tareas:

- Calibrado y/o diagnóstico de canales analógicos

- Medida de la temperatura interna y la humedad del GDP-32<sup>II</sup>.

- Medida de la resistencia del electrodo

El circuito del multiplexor consiste en suministro de energía, DAC de alta linearidad de 16 bit y un multiplexor de cuatro puertos. El suministro de energía a esta tarjeta y un canal analógico deben estar conectados para que este circuito funciones y la salida multiplexada pueda ser leída. El multiplexor selecciona una de las 4 señales analógicas:

- a) Convertidor Digital a Analógico (DAC) El DAC de 16 bit DAC en la placa de Calibrado y Sincronización genera un voltaje en continua entre -8.35 y +8.35 voltios requerido por las señales digitales de control. La selección del puerto DAC proporciona este nivel al sistema de bus de calibrado. Esto lo hace disponible para todas las tarjetas de entrada analógica. Este voltaje en continua se usa para un calibrado preciso de la ganancia del sistema.

- b) Calibrado La selección de esta entrada permite adaptar el voltaje generado por el DAC a la frecuencia seleccionada por la placa de sincronización, generando así una señal positiva y negativa. La señal generada es una señal en el dominio de la frecuencia o del tiempo determinada por el ciclo configurado en la placa de sincronización.

- c) **Temperatura** Esta entrada es un voltaje proporcional a la temperatura interna del instrumento en °C.

- d) **Humedad** Esta entrada es un voltaje proporcional a la humedad relativa interna en %.

#### **ÓHMETRO**

El circuito del óhmetro proporciona un nivel de corriente constante al bus de calibrado. Un suministro de energía aislado proporciona energía al óhmetro. Cuando este relé se enciende, la alimentación de Calibrado, si está encendida, se apaga y el relé de salida se posiciona en OHM. El nivel de corriente constante es seleccionable a 1.0 ma o 0.1 ma.

#### SECCIÓN DE SINCRONIZACIÓN

La función primaria de la sección de sincronización es el *Generador de Frecuencia* que genera señales de sincronismo precisas requeridas para la digitalización y detección síncrona a 24 frecuencias binarias ( $2^{-10} \le f \le 2^{-13}$  Hz). También hay un *Reloj en Tiempo Real* que proporciona una base de tiempo más precisa que el reloj del MPU.

#### Generador de Frecuencia

El generador de frecuencia divide la frecuencia 4.980736 MHz <sup>1</sup> del oscilador principal en frecuencias binarias que representan la detección fundamental de frecuencias por el receptor GDP-32<sup>II</sup>. Correspondiendo a cada una de las 24 frecuencias seleccionables, hay 3 rangos de pulsos sincrónicos relevantes:

- a) **Periodo** Un ciclo con rango del 100% a la frecuencia seleccionada.

- b) **Cyclo de Ocupación (Duty Cycle)** Un ciclo con rango del 100% al doble de la frecuencia seleccionada. Esta frecuencia se usa para la modulación actual en el dominio del tiempo y para indicar sincronización con corriente ON y corriente OFF para la adquisición de datos en el dominio del tiempo.

- c) **Muestreo** Esta frecuencia de pulso proporciona al convertidor ADC un comando que se usa para la adquisición de datos a la frecuencia base seleccionada.

Bajo control del MPU, las frecuencias apropiadas se seleccionan para dirigir las placas analógicas, y el transmisor I/O.

#### Reloj en Tiempo Real

Un segundo ASIC se ha añadido a la BD244 y BD288, proporcionando un reloj en tiempo real conducido por la frecuencia 2.490368 MHz. Este reloj se configura por el GDP-32<sup>II</sup> y a partir de entonces, los datos se van almacenando con la consigna de tiempo del BD244/288 antes que con la placa menos precisa MPU (que se ejecuta bajo ROM-DOS). Este reloj en tiempo real se añadió para proporcionar un referencia de tiempo absoluta para facilitar la obtención de datos en series sincrónicas con múltiples receptores, y para habilitar la sincronización con el sistema GPS (BD288).

#### **Receptor GPS**

Una placa GPS basada en PCI-4 puede instalarse para imponer disciplina al cristal de 4.980736 MHz. También proporcionar la sincronización de múltiples GDP-32<sup>II</sup>, así como información acerca de la posición.

El GDP-16 y su predecesor, el GDP-12 se fabricaron con osciladores de 5.0 MHz, una frecuencia que no puede usarse para generar frecuencias binarias exactas usando la división entera. De este modo, mientras que las frecuencias generadas son nominalmente las mismas, para los propósitos de detección sincrónica son diferentes. Por esto, los instrumentos GDP/XMT-32 no pueden usarse junto con generaciones anteriores de instrumentos GDP/XMT sin cambiar las frecuencias de los antiguos cristales de 5.0 MHz a 4.980736 MHz. La frecuencia del oscilador de cristal se cambió para conseguir una mejora significativa en el rechazo de ruido a las frecuencias deseadas.

### **SMALL CASE**

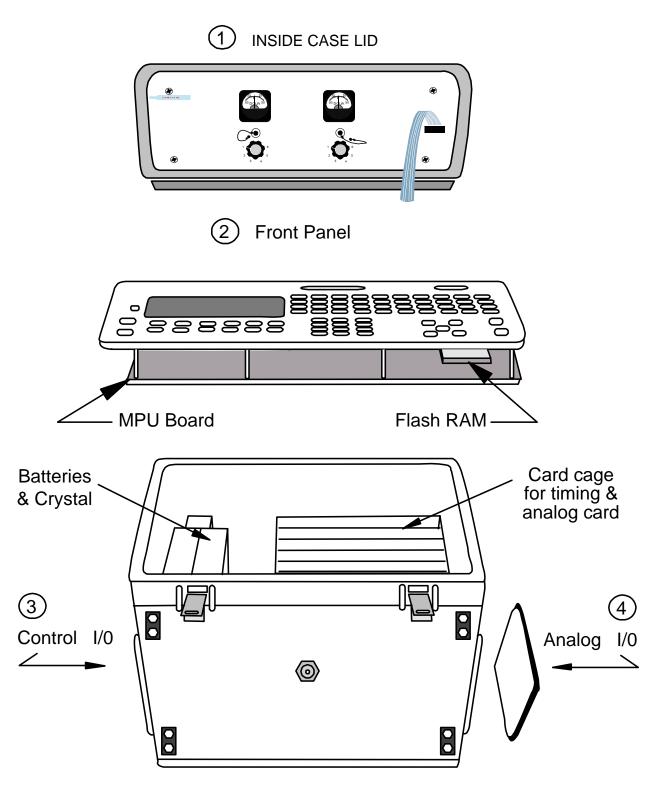

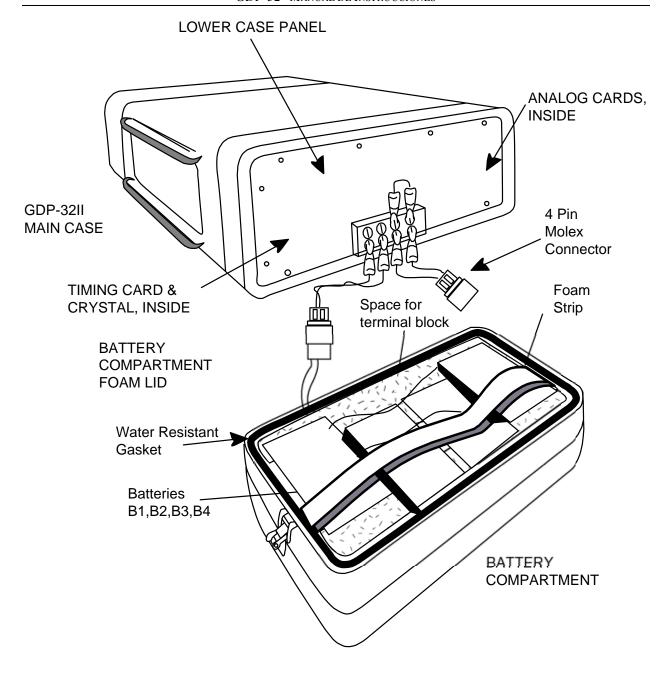

Figura 16.7 – GDP-32<sup>II</sup> de Caja o Carcasa Pequeña

# LARGE CASE Inside O CASE GROUND Case Lid Front Panel MPU Board Flash RAM Mother board & card cage for timing & analog cards Analog Control I/O Panel I/0 Panel

Figura 16.8 (a) - GDP-32<sup>II</sup> de Caja o Carcasa Grande

Figura 16.8 (b) - Compartimento de la Batería en el GDP-32<sup>II</sup> de Caja Grande

#### 16.7 EL COMPARTIMENTO DE LA BATERÍA

#### DISEÑO EN CAJA PEQUEÑA (GDP-32<sup>II</sup>T)

Al compartimento de la batería se accede desde la parte superior de la caja quitando el panel frontal. Este compartimento contiene 2 baterías de 6 voltios, 10 amperios-hora conectadas en serie para proporcionar 12 voltios con capacidad de 10 amperios-hora.

Para hacer el mantenimiento del compartimento de la batería, quite el panel frontal y los 4 tornillos cabeza phillips #6-32 que aseguran la tapa del compartimento a la caja de la batería.

#### DISEÑO DE CAJA GRANDE

El compartimento de la batería en la caja grande del GDP-32<sup>II</sup> se conecta a la parte inferior de la caja del receptor por clips de cierre. Hay cuatro baterías de 6 voltios, cableadas en serie y paralelo para proporcionar 12 voltios y 20 amperios-hora.

El Panel inferior se puede retirar para permitir el acceso a la parte inferior de la caja principal. Hay fusibles de 4 amperios protegiendo el suministro principal de 12 v. Los fusibles de repuesto están dentro del panel de la caja inferior en todos los nuevos GDP-32<sup>II</sup>.

Lea la *Sección 17.5* antes de intentar quitar directamente las baterías de la caja grande.

**NOTA:** Si una batería va mal, a menudo es recomendable reemplazar el juego completo de baterías, antes que reemplazar una sola batería.

Una junta de goma proporciona un sellado a prueba de agua. La conexión eléctrica se produce a través de uno de dos conectores de 3 hilos montados sobre el panel de la caja inferior. Las baterías se pueden enchufar en cualquier conector. El segundo conector se usa para conectar un juego de baterías de repuesto antes de desconectar el juego de baterías actual, de manera que no se interrumpa la sincronización de los circuitos.

El voltaje de la batería se comprueba antes de cada ciclo de adquisición de datos. Se muestra en la parte superior de la pantalla LCD. Cuando el voltaje de la batería cae por debajo de 11.2 voltios, aparece un mensaje de aviso, y el usuario dispone de 10 a 20 minutos antes de que el cortacircuitos desconecte.

Los dos modelos en caja grande y pequeña del GDP-32<sup>II</sup> contienen un cortacircuitos electrónico situado en la placa del panel frontal (BD287) que desconecta la alimentación cuando el voltaje de la batería cae por debajo de 10.6 voltios o sube por encima de 15.5 voltios.

Vea la Sección 17.5 para información sobre comprobación y reemplazo de baterías.

#### 16.8 EL OSCILADOR DE CRISTAL

Toda la sincronización del GDP-32<sup>II</sup> se basa en un *Oscilador de Cristal de Cuarzo* a 4.980736 MHz (*ver nota en 16.19*). El Oscilador de Cristal va montado directamente sobre la placa de calibrado y sincronización en la caja grande GDP-32<sup>II</sup>. En la caja pequeña GDP-32<sup>II</sup>T, va montado al lado o encima del compartimento para baterías.

La alta precisión del cristal sirve permite ajustes eléctricos y mecánicos. El ajuste eléctrico del cristal se explica en la *Sección 6.2* y el ajuste mecánico se describe en la *Sección 17.6*.